# Transistor-Clamped H-Bridge Based Cascaded Multilevel Inverter With New Method Of Capacitor Voltage Balancing

### A Srinivasan.

M.Tech, Student [Power electronics] DEPT OF EEE, SVPCET- PUTTUR, AP

### M Lokanadam,

Asst. Professor, DEPT OF EEE, SVPCET- PUTTUR, AP

**Abstract:** This paper presents a three-phase cascaded mul-tilevel inverter that uses five-level transistor-clamped H-bridge power cells. Multicarrier phase-shifted pulse-width modulation method is used to achieve balanced power distribution among the power cells. A new method to balance the midpoint capacitor voltage in each cell is developed and tested. The analysis of the output voltage harmonics and the total power losses covering the conduction and the switching power losses are carried out and compared with the cascaded neutral-point-clamped and the conventional cascaded H-bridge inverters. For verifications, the proposed inverter is experimentally tested on an induction motor. From the results, the proposed inverter provides higher output quality with relatively lower power loss as compared to the other conventional inverters with the same output quality.

**Index Terms:** Cascaded H-bridge, cascaded neutral-point-clamped inverter, five-level inverter, multicarrier phase-shifted pulse-width modulation (CPS-PWM), multilevel inverter, transistor-clamped converter.

#### I. INTRODUCTION

DEMAND for high-voltage, high-power converters capable of producing high-quality waveforms while utilizing low-voltage devices and reduced switching frequencies has led to the multilevel inverter development with regard to semiconduc-tor power switch voltage limits. Multilevel inverter research is ongoing to further improve its capabilities, to optimize control techniques, and to minimize both component count and man-ufacturing cost. Owing to voltage limits, to enable high-power conversion, power switches are typically cascaded in series and configured into multilevel structures. The synthesized multi-level outputs are superior in quality which results in reduced filter requirements and overall system size. Switching losses are also reduced, with lower switching frequency operation and maintained high-power quality.

The multilevel inverter has been implemented in various applications ranging from medium to high-power levels, such as motor drives [1]–[3], power conditioning devices [4], [5] also conventional or renewable energy generation and distribution

[6]–[8]. There are three major multilevel voltage source in-verters topologies, namely neutral-point-clamped (NPC) or the diode-clamped inverter [9], cascaded multilevel [10], and flying capacitor (capacitor clamped) [11]. There are also topologies that have been introduced and have successfully found var-ious industrial applications [12]–[14]. Modulation strategies applied to multilevel inverters are selective harmonics elimi-nation [15]–[17] carrier-based pulse-width modulation (PWM) [18]–[22], space vector modulation (SVM) [23]–[26], and stair-case or fundamental frequency modulation [27], [28].

This paper focuses on the cascaded multilevel inverter topol-ogy. Generally, among the three topologies, the cascaded mul-tilevel inverter has the potential to be the most reliable and achieve the best fault tolerance owing to its modularity; a feature that enables the inverter to continue operating at lower power levels after cell failure [29]–[31]. Modularity also per-mits the cascaded multilevel inverter to be stacked easily for high-power and high-voltage applications. The cascaded multi-level inverter typically comprises several identical single phase H-bridge cells cascaded in series at its output side. This config-uration is commonly referred to as a cascaded H-bridge (CHB), which can be classified as symmetrical if the dc bus voltages are equal in all the series power cells, or as asymmetrical if oth-erwise. In an asymmetrical CHB, dc voltages are varied to pro-duce more output levels [2], [32]. Consequently, inverter design becomes more complicated as each power cell has to be sized accordingly to the different power levels, including isolated dc sources. This makes symmetrical CHB modularity advanta-geous over asymmetrical with regard to maintenance and cost.

For the symmetrical cascaded inverter, voltage level increase is possible without varying dc voltage with the same number of power cells, as proposed by this paper. Recently, the transistor-clamped converter topology has received increased attention as it provides a simpler approach to increase output levels by taking different voltage levels from the series stacked capacitors [12], [33]. In this paper, the proposed new

configuration uses a five-level transistor-clamped H-bridge (TCHB) as a power cell that can produce a five-level output instead of three-level as with the conventional H-bridge [33]–[35]. A similar arrange-ment using a NPC in each power cell has been presented [3]. However, an excessive number of power switches and diodes are required. In [19], though the number of switches for each cell is lower, and to achieve the same output quality, more cells are required, which increases the number of isolated dc sources, as well as bulky transformers.

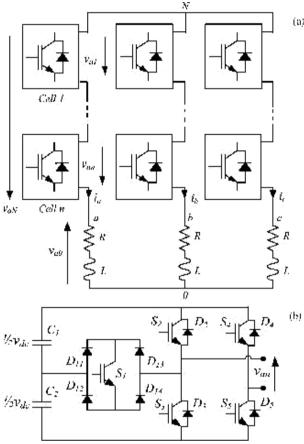

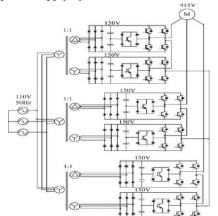

Fig. 1. TCHB: (a) general configuration of the proposed three-phase cascaded multilevel inverter and (b) topology of five-level transistor-clamped H-bridge for each cell.

In this paper, the proposed inverter is evaluated for medium-voltage drive application, in which based on the standard voltages, 2.3 kV to 13.8 kV and the power range 400 kW to 40 MW [36]. With more output levels, in addition to better output quality, the possibility of motor insulation failure as a result of steep voltage wave fronts (dv/dt) across the motor terminals is reduced, compared to the conventional CHB with similar cell configuration [29]. Focus was more on constant-speed drive applications such as fans, blowers, pumps, and compressors, since these comprise 97% of currently installed medium-voltage drives [37]. It is found in various industries such as production plants, process industries, as well as in the oil and gas sectors. Simulation and experimental results are presented for verification. This paper is organized as fol-lows: the inverter's configuration is presented in Section II, the PWM modulation strategy in Section III, analysis of output voltage and harmonics in Section IV, the proposed capacitor voltage balancing in Section V, comparison with several con-ventional inverters in Section VI, experimental verification in Section VII, and Section VIII is the conclusion.

#### II. PROPOSED INVERTER CONFIGURATION

Fig. 1(a) is the general configuration of the proposed in-verter, comprising  $N_C$  series-connected five-level TCHB cells.

## TABLE I FIVE-LEVEL TRANSISTOR-CLAMPED H-BRIDGE OUTPUT VOLTAGE

| $S_I$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | v <sub>an</sub>      |

|-------|-------|-------|-------|-------|----------------------|

| 0     | 1     | 0     | 0     | 1     | $v_{dc}$             |

| 1     | 0     | 0     | 0     | 1     | $\frac{1}{2}v_{dc}$  |

|       | 0     | 1     | 0     | 1     |                      |

| 0     | or    | or    | or    | or    | 0                    |

|       | 1     | 0     | 1     | 0     |                      |

| 1     | 0     | 0     | 1     | 0     | $-\frac{1}{2}v_{dc}$ |

| 0     | 0     | 1     | 1     | 0     | $-v_{dc}$            |

(Switch ON = 1, Switch OFF = 0)

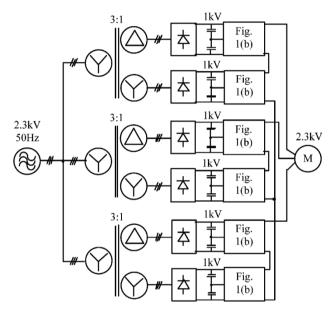

Fig. 2. Basic configuration for medium-voltage drive application.

Fig. 1(b) shows the cell with the additional one bidirectional switch connected between the first leg of the H-bridge and the capacitor midpoint, enabling five output voltage levels ( $\pm v_{dc}$ ,  $\pm (1/2)v_{dc}$ , 0) to be produced based on the switch combinations given in Table I. The basic configuration for a 2.3-kV medium-voltage drive is shown in Fig. 2 where each power switch is a single 1.7-kV IGBT. The number of power cells required depends mainly on the operating voltage and production cost. In this case, a two-cell configuration is suf-ficient to produce a high-quality output with up to 17-voltage levels.

In general, the maximum levels in the phase and line voltages of the proposed inverter, based on  $N_C$  cells, are given by the following equations:

$$\eta_{12} = 4N_C + 1 \tag{1}$$

$$m = 8N_C + 1.$$

(2)

Based on valid switch combinations,  $S_1 = -S_5$  in Table I, the cell output voltage  $v_{an}$  can be represented by

$$v = v_{dc}(S_{5n} - S_{4n}) \frac{1}{2} S_{1n}^{-+} + |S_{2n} - S_{4n}| |.|S_{3n} - S_{5n}|_{\infty}$$

(3)

Summation of all the power cell voltages gives the phaseto-neutral voltage, XaN and line voltage, Xab, respectively, as

$$\begin{array}{c}

N_C \\

n=1

\end{array}$$

$$- \\

y_{ab} = y_{aN} - y_{bN}.$$

(4)

#### III. PWM MODULATION STRATEGY

The modulation index M of the proposed multilevel inverter is defined by

$$M = \frac{1 V}{2 V_{Gk}}$$

(6)

where  $V_{\text{ref}}$  is the amplitude of the voltage reference and  $V_{Cr}$  is the amplitude of the carrier signal. Multicarrier phase-shifted PWM (CPS-PWM) modulation is used to generate the PWM signals. The amplitude and frequency of all triangular carriers are the same as well as the phase shifts between adjacent carriers. Depending on the number of cells, the carrier phase shift for each cell  $\theta_{Cr,n}$  can be obtained from

$$\theta_{Cr,n} = \frac{2\pi(n-1)}{n-1}, \quad n=1, 2 \dots N_{C_n}$$

(7)

For signal generation in each cell, two voltage references and one carrier signal are used [18]. The references,  $v_{refl}$  and  $v_{ref2}$  are derived from a full-wave voltage reference,  $v_{ref}$  defined by

Both references are identical but displaced by an offset equal to the carrier's amplitude which is 1/2. When the voltage reference is between  $0 < v_{ref} \le (1/2)$ ,  $v_{ref1}$  is compared with the triangular carrier and alternately switches  $S_1$  and  $S_3$  while maintaining  $S_5$  in the on state to produce either  $(1/2)v_{dc}$  or 0. Whereas, when the reference is between  $(1/2) < v_{ref} \le 1$ ,  $v_{ref2}$  is used and alternately switches  $S_1$  and  $S_2$  while main-taining  $S_5$  in the on state to produce either  $(1/2)v_{dc}$  or  $v_{dc}$ . As for the reference between  $-(1/2) < v_{ref} \le 0$ ,  $v_{ref1}$  is used for comparison which alternately switches  $S_1$  and  $S_2$  while maintaining  $S_4$  in the on state to produce either  $-(1/2)v_{dc}$  or 0. For a voltage reference between  $-1 < v_{ref} \le -(1/2)$ ,  $v_{ref2}$  is compared with the carrier to produce either  $-(1/2)v_{dc}$  or  $-v_{dc}$  alternately switches  $S_1$  and  $S_3$ , maintaining  $S_4$  in the on state. It is noted that two switches,  $S_4$  and  $S_5$ , only operate in each reference half cycle. This implies that both switches operate at the fundamental frequency while the others operate close to the carrier frequency. This allows the dc voltage to be switched at a low frequency so as to reduce the switching losses.

0.5 Vcr1 ---- Vret2 --- Vret1 ---- Vret2 0.005 0.01 0.015 0.02

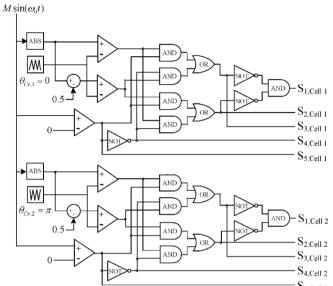

Fig. 3. Multicarrier phase-shifted PWM for two-cell configuration

Fig. 4. PWM signal generation with multicarrier phase-shifted modulation for phase a.

TABLE II

PHASE-TO-NEUTRAL VOLTAGE FOR TWO-CELL CONFIGURATION

|                               | $v_{al}$             | $v_{a2}$             | $v_{aN}$                   |

|-------------------------------|----------------------|----------------------|----------------------------|

| 0                             | 0                    | 0                    | 0                          |

|                               | ½v <sub>dc</sub>     | 0                    | 1/2 <i>v</i> <sub>dc</sub> |

| $0 < v_{ref} \leq^1/2$        | 0                    | $\frac{1}{2}v_{dc}$  | ¹/₂v <sub>dc</sub>         |

|                               | $\frac{1}{2}v_{dc}$  | $\frac{1}{2}v_{dc}$  | $v_{dc}$                   |

|                               | $\frac{1}{2}v_{dc}$  | $\frac{1}{2}v_{dc}$  | $v_{dc}$                   |

| $^{1}/_{2} < v_{ref} \le 1$   | $v_{dc}$             | $\frac{1}{2}v_{dc}$  | $^{3/2}v_{dc}$             |

| /2~Vref≥1                     | $\frac{1}{2}v_{dc}$  | $v_{dc}$             | $^{3}/_{2}v_{dc}$          |

|                               | $v_{dc}$             | $v_{dc}$             | $2v_{dc}$                  |

|                               | 0                    | 0                    | 0                          |

| $-^{1}/_{2} < v_{ref} \le 0$  | $-\frac{1}{2}v_{dc}$ | 0                    | $-\frac{1}{2}v_{dc}$       |

| $-7_2 \sim V_{ref} \succeq 0$ | 0                    | $-\frac{1}{2}v_{dc}$ | $-\frac{1}{2}v_{dc}$       |

|                               | $-\frac{1}{2}v_{dc}$ | $-\frac{1}{2}v_{dc}$ | $-v_{dc}$                  |

|                               | $-\frac{1}{2}v_{dc}$ | $-\frac{1}{2}v_{dc}$ | $-v_{dc}$                  |

| $-1 < v_{ref} \le -1/2$       | $-v_{dc}$            | $-\frac{1}{2}v_{dc}$ | $-3/2v_{dc}$               |

| $-1 \sim V_{ref} \simeq -/2$  | $-\frac{1}{2}v_{dc}$ | $-v_{dc}$            | $-3/2v_{dc}$               |

|                               | $-v_{dc}$            | $-v_{dc}$            | $-2v_{dc}$                 |

Fig. 3 shows the modulation scheme used for the proposed two-cell configuration and Fig. 4 shows a detail block diagram for generating the PWM signals. The phase-to-neutral volt-age  $v_{aN}$  obtained based on the voltage reference magnitude and the combination of cell voltages,  $v_{a1}$  and  $v_{a2}$ , are listed in Table II.

From Table II, a total of nine-levels  $(\pm 2v_{\rm dc}, \pm (3/2)v_{\rm dc}, \pm v_{\rm dc}, \pm (1/2)v_{\rm dc}, 0)$  phase-to-neutral voltages are produced when both cells are cascaded with CPS-PWM modulation. When  $v_{\rm ref}$  is within  $0 < v_{\rm ref} \le (1/2)$ , each cell can only pro-duce 0 or  $(1/2)v_{\rm dc}$ ; therefore,  $v_{aN}$  has three possible outputs which are 0,  $(1/2)v_{\rm dc}$ , and  $v_{\rm dc}$ . In the case of  $(1/2) < v_{\rm ref} \le 1$ , each cell can produce either  $(1/2)v_{\rm dc}$  or  $v_{\rm dc}$  which result in three possible  $v_{aN}$  outputs also,  $v_{\rm dc}$ ,  $(3/2)v_{\rm dc}$ , and  $2v_{\rm dc}$ . For negative  $v_{\rm ref}$ , the outputs are similar but with the opposite polarity. As the phase voltages are displaced by  $(2/3)\pi$  from other, higher levels of line voltages will be generated where for  $v_{ab}$ , obtainable from (5).

#### IV. ANALYSIS OF OUTPUT VOLTAGE AND HARMONICS

In general, any PWM switched waveform can be expressed in infinite series of sinusoidal harmonics form as

$$F(I) = -^{n} \cup 0 + \frac{A_{0m} \cos(n\omega_{o}I) + B_{0m} \sin(n\omega_{o}I)}{n=1}$$

$$0 - \frac{A_{m0} \cos(m\omega_{o}I) + B_{m0} \sin(n\omega_{o}I)}{n=1}$$

$$0 - \frac{A_{m0} \cos(m\omega_{o}I) + B_{m0} \sin(n\omega_{o}I)}{n=1}$$

$$0 - \frac{A_{mn} \cos(m\omega_{o}I) + B_{m0} \sin(n\omega_{o}I)}{n=1}$$

$$1 - \frac{A_{mn} \sin(m\omega_{o}I + n\omega_{o}I)}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

$$1 - \frac{A_{mn} + jB_{mn}}{n=1} = \frac{2\pi^{2} - F(x, y)e^{j(mx+ny)} dxdy}{n=1}$$

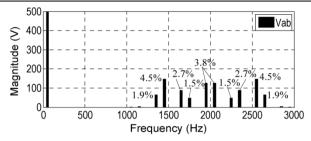

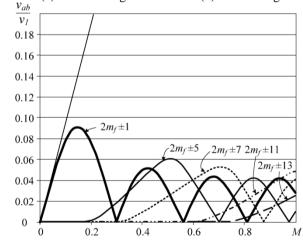

Based on the method developed in [38], the expression for instantaneous  $v_{aN}$  and instantaneous  $v_{ab}$  of the proposed inverter configuration can be represented by the following equations where J represents the Bessel function of the first kind. From these equations, the harmonic spectrum for both  $v_{aN}$  and  $v_{ab}$  can be obtained at various operating conditions. Evaluating

(14) with

$$N_C = 2$$

,  $M = 0.95$ ,  $v_{dc} = 1$  kV,  $f_0 = 50$  Hz, and  $f_c = 1$  kHz results in the line voltage harmonics shown in Fig. 5

$$v_{aN}(t) = N_C M v_{dc} \cos(\omega_o t) + \frac{v_{dc}}{\pi} \times m = 1 \quad n = -\infty$$

$$1 \qquad \qquad --$$

$$\times \overline{m} \qquad J_{2n-1}(2N_C m \pi M) \cos((2N_C m + n + 1)\pi)$$

$$\times \cos(N_C m \omega_c t + (2n - 1)\omega_o t) - (13)$$

$$- \frac{\pi}{m} \qquad \frac{2v_{dc}}{\kappa + \pi} \times m = 1 \quad n = -\infty$$

$$1 \qquad \qquad --$$

$$\times \overline{m} \qquad J_{2n-1}(2N_C m \pi M) \cos((2N_C m + n + 1)\pi)$$

$$1 \qquad \qquad \times \sin(2n - 1) \qquad \overline{3} \quad \pi$$

$$1 \qquad \qquad \times \sin(2n - 1) \qquad \overline{3} \quad \pi$$

$$1 \qquad \qquad \times \sin(2n - 1) \qquad \overline{3} \quad \pi$$

$$1 \qquad \qquad \times \sin(2n - 1) \qquad \overline{3} \quad \pi$$

$$1 \qquad \qquad (14)$$

Fig. 5. Harmonic spectrum of line voltage generated using (14). each

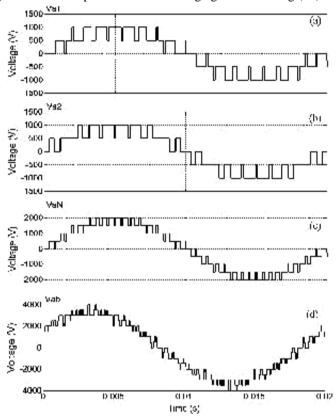

Fig. 6. Simulated output voltage of the proposed inverter. (a) Cell 1 output voltage. (b) Cell 2 output voltage. (c) Phase voltage. (d) Line voltage.

The simulated output voltages for the medium-voltage drive configuration in Fig. 2 are shown in Fig. 6. Test conditions were the same for comparison. Similarly, the modulating signal's frequency and modulation index were 50 Hz and 0.95, respectively. The triangular carriers have a maximum switching frequency of 1 kHz and are phase-shifted 180° to each other.

All the cells were supplied by 1-kV dc voltages. The phase and line voltages have twice the switching frequency of each cell, following the number of cells cascaded. The frequency components of these voltages obtained from Matlab simulation are shown in Fig. 7. The detailed harmonic content of the line voltage versus modulation index is shown in Fig. 8.

#### V. PROPOSED CAPACITOR VOLTAGE BALANCING

During normal operation, natural balancing can be achieved in each cell, keeping the midpoint capacitor voltage close to

Fig. 7. Harmonic spectrum of the proposed inverter. (a) Cell 1 output voltage harmonics. (b) Cell 2 output voltage harmonics. (c) Phase voltage harmonics. (d) Line voltage harmonics.

Fig. 8. Line voltage harmonics versus modulation index  $(m_f = f_c/f_o)$ .

$(1/2)v_{dc}$ . However, under certain circumstances such as during a transient or sudden large disturbance, cells may become im-balanced, causing the average current drawn from the midpoints to be nonzero, therefore, shifting the midpoint capacitor voltage away from  $(1/2)v_{dc}$ . In a worst case scenario, this may lead to system instability and cause damage to the whole system. The

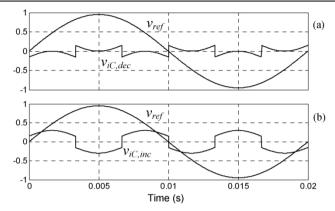

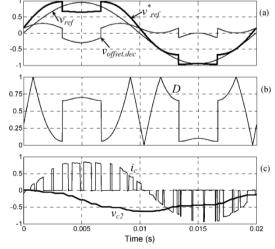

Fig. 9. Third harmonic offsets. (a) Offset voltage to decrease the midpoint capacitor current. (b) Offset voltage to increase the midpoint capacitor current.

average current,  $I_{avg}$  can be obtained through integration of the capacitor current over one fundamental period

$$I = \int_{\text{avg}}^{2\pi} 2\pi \int_{0}^{2\pi} i_{C}(t) dt.$$

(15)

In order to ensure reliable and safe system operation, cell balancing control has to be incorporated [39]. In this case, switching state redundancy is not applicable since PWM modu-lation is used. Moreover, the absence of a bidirectional switch in the second leg of the TCHB limits the cell balancing capability under certain conditions even if the SVM modulation is used. In addition to using balancing circuitry, voltage balancing can be implemented by controlling  $I_{\rm avg}$  via a third harmonic offset injection method [40]. This method uses two offset voltages,  $v_{iC}$  , dec and  $v_{iC}$  , inc, as shown in Fig. 9(a) and (b). These offset voltages can be represented by the following equations:

$$\begin{array}{ll}

^{\nu}i_{C} \\

, \text{dec} \\

& \text{voffset,pk} \quad \sin^{3}\omega^{t} \\

&= \quad \begin{array}{ll}

^{-\nu}\text{offset,dc'} & \text{if } \nu_{\text{offset,pk}} \sin 3\omega t \geq 0 \\

& \quad \text{voffset,pk} \quad \sin^{3}\omega^{t} \\

& \quad \text{+}^{\nu}\text{offset,dc'} & \text{If } \nu_{\text{offset,pk}} \sin 3\omega t < 0

\end{array}$$

$$\begin{array}{ll}

\nu_{iC,\text{inc}} & \nu_{\text{offset,pk}} \sin^{3}\omega t \\

& \quad \text{voffset,dc'} & \text{if } \nu_{\text{offset,pk}} \sin 3\omega t \geq 0 \\

& \quad \text{voffset,pk} \quad \sin^{3}\omega^{t} \\

& \quad \text{-}^{\nu}\text{offset,dc'} & \text{If } \nu_{\text{offset,pk}} \sin 3\omega t < 0

\end{array}$$

$$\begin{array}{ll}

\nu_{iC,\text{inc}} & \nu_{\text{offset,pk}} \sin 3\omega t \geq 0 \\

& \quad \text{voffset,pk} \sin 3\omega t \leq 0

\end{array}$$

$$\begin{array}{ll}

\nu_{iC,\text{inc}} & \nu_{\text{offset,pk}} \sin 3\omega t \leq 0 \\

& \quad \text{voffset,pk} \sin 3\omega t \leq 0

\end{array}$$

where  $v_{\text{offset,pk}}$  and  $v_{\text{offset,dc}}$  are two variables for controlling its amplitude and dc offset. Adding any of these offsets to the voltage reference changes the duty cycle D of the midpoint capacitor current and also its amplitude

$$D = 2 (1 - abs(v_{ref})), \text{ if } \frac{1}{2} \leq abs(v_{ref}) \leq \frac{1}{2}$$

$$2abs(v_{ref}), \text{ if } 0 \leq abs(v_{ref}) \leq 2$$

$$(18)$$

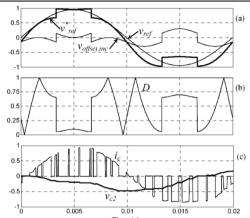

Fig. 10. (a) Proposed offset voltage to increase the midpoint capacitor voltage and the corresponding voltage reference, (b) duty cycle, (c) midpoint capacitor current and voltage.

Maximum D occurs when the voltage reference is 1/2 and minimum when the reference is 0 or 1. Adding the offset voltage in Fig. 9(a) forces the voltage reference away from 1/2, reducing the duty cycle and thus the midpoint capacitor current. Whereas, adding the offset voltage in Fig. 9(b) forces the reference close to 1/2 and therefore increases the midpoint capacitor current.

In each cell, to regulate the midpoint capacitor voltage, combinations of these offset voltages are used. Using only one offset voltage in one fundamental period as was done for a diode-clamped back-to-back converter in [40] is not applicable, since the capacitor current varies by the same amount in both half cycles, producing  $I_{\text{avg}} \equiv 0$  and therefore resulting in no voltage balancing. Whereas, use of a different offset voltage in each half cycle of the fundamental period as proposed in this paper produces positive or negative  $I_{\text{avg}}$ , depending on the combination used. For instance, using the combination of  $v_{iC}$ , dec in the positive half cycle and  $v_{iC}$ , inc in the negative half cycle produces a negative  $I_{\text{avg}}$  so as to increase the midpoint capacitor voltage, and vice versa

$$v = {}^{v}i_{C}, \text{dec} \quad 0 < \omega t \leq \pi$$

offset, in

$$c = {}^{v}i_{C}, \text{inc} \quad \pi < \omega t \leq 2\pi$$

$$v = {}^{v}i_{C}, \text{inc} \quad 0 < \omega t \leq \pi$$

offset, d

$$ec = {}^{v}i_{C}, \text{dec} \quad \pi < \omega t \leq 2\pi.$$

(20)

The effective region for controlling the midpoint capacitor current in this approach is  $(1/3)\pi \le \omega t \le (2/3)\pi$  in the pos-itive half cycle and  $(4/3)\pi \le \omega t \le (5/3)\pi$  in the negative half cycle. In order to provide an efficient control of cell balancing while keeping the output distortion minimal,  $v_{\text{offset,pk}}$  and  $v_{\text{offset,dc}}$  are set such that the modulated voltage reference will be close to 1 when the maximum modulation index is applied.

Fig. 11. (a) Proposed offset voltage to decrease the midpoint capacitor voltage and the corresponding voltage reference, (b) duty cycle, and (c) midpoint capacitor current and voltage.

ISSN: 2455-4847

www.ijlemr.com || REETA-2K16 || PP. 477-498

Incorporating  $v_{\text{offset}}$  for cell balancing defines the new voltage reference as

$$v_{\text{ref}}^* = M \sin \omega t + v_{\text{offset(inc or dec)}}$$

(21)

Figs. 10 and 11 show the offset voltages used for both cases with their corresponding voltage references, duty cycles, and midpoint capacitor currents and voltages. From both figures, it is noted that the midpoint capacitor voltage increases or decreases after one fundamental period as a result of adding the corresponding  $v_{\text{offset}}$ .

The variation of the midpoint capacitor voltage depends on the load current applied to the inverter. For a given power, operating voltage and power factor, the load current  $I_I$  can be calculated as follows:

$$P$$

$$I_L = \sqrt{3V \cos \theta} . \tag{22}$$

The midpoint capacitor current  $i_C$  can be estimated by multi-plying the duty cycle D with the instantaneous load current,  $i_L$ . Accordingly, this yields capacitor voltage variation as

$$\frac{1}{v_C \approx C} \frac{i_L}{c_1 dt} = \frac{i_L D}{c_2 DT_s} = \frac{i_L D}{c_1 f_s}$$

(23)

where  $f_s$  is the switching frequency, which is also equal to the carrier frequency. The duty cycle is obtained by substituting the corresponding  $v_{ref}^*$  into (18), depending on which balancing action is required, either to increase or decrease the midpoint capacitor voltage. Since PWM modulation is used, voltag variation in each switching cycle can be obtained by rewriting (23) in discrete form as follows:

$$v_c(k) \approx \frac{i_L(k)}{c} D(k) T_s = \frac{i_L(k)D(k)}{c f_s}$$

(24)

Accordingly, voltage variation in one fundamental period can be obtained from (25), where  $N_k$  is the number of switching cycle in one fundamental period defined as  $f_s/f_0$

e

$$N_k$$

$N_k$

$N_k$

From (25), it is obvious that the voltage variation is directly proportional to the load current while inversely proportional to the capacitance and the switching frequency, for a fixed modulation index. It is interesting to note how the midpoint ca- pacitor voltage varies when a different modulation index of the voltage reference is applied, keeping the same values of offset variables (i.e.,  $v_{\rm offset,pk}$  and  $v_{\rm offset,dc}$  are both set to 0.15). For comparison at a different modulation index, the same amplitude of load current is used. The reason is that the new voltage reference defined using different modulation index produces a different duty cycle. As a result, different midpoint capacitor current is obtained in each case, thus indirectly evaluating the performance of the cell balancing mechanism at different loading conditions.

Fig. 12(a) shows the variation of the midpoint capacitor voltage versus modulation index for several capacitance values in one fundamental period at 1-kHz switching frequency and with a unity power factor. Relative comparison is made against the balancing condition at M=1 which represents 1-MW load. This is based on the configuration shown in Fig. 2, and the result is normalized to  $v_{\rm dc}=1$  kV. The result is applicable to both balancing conditions since the offset voltages are interchanged between the positive and negative half cycle. This means that, the result can be inferred as the amount of voltage increments or decrements, depending on the balancing condition. Fig. 12(b) shows the voltage variation at different switching frequencies; 1 kHz, 1.5 kHz, and 2 kHz when using 3400  $\mu$ F capacitor. The effect of the cell balancing mechanism at different power factor is shown

in Fig. 12(c) for 1-kHz switching frequency with the same capacitance. Based on the results obtained, the highest voltage variation occurs when the modulation index is 0.8. Depending on the depth of imbalance,

the balancing time  $\tau_{\text{bal}}$  in terms of the number of cycles required can be obtained by dividing the depth of imbalance  $\varepsilon$

normalized to  $v_{\rm dc}$  with  ${}^{\nu}c$ , cycle  ${}^{\nu}$ dc

$${}^{\tau}\text{bal} = \frac{\mathcal{E}}{{}^{\nu}c, \text{cycle}}.$$

(26)

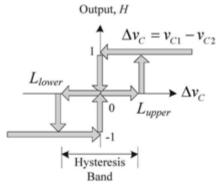

A hysteresis controller as shown in Fig. 13 is used to realize the voltage balancing mechanism where the control is activated only when the capacitor voltage difference,  $v_C$  has exceeded the hysteresis band limits. When  $v_C$  exceeds the

Fig. 12. Simulation results showing the variation of the midpoint capacitor voltage in one fundamental period for different (a) capacitance values, (b) switching frequencies, and (c) power factors.

Fig. 13. Hysteresis controller for the cell balancing mechanism

upper limit,  $L_{\text{Upper}}$  (i.e.,  $v_{C1}$   $v_{C2}$ ) the hysteresis controller sets the output H=1, and therefore  $v_{\text{offset,inc}}$  is added to the voltage reference to increase the midpoint capacitor voltage until  $v_C=0$ , and vice versa. Under natural balancing, the midpoint capacitor voltage fluctuates within the band limits, keeping the controller setting H=0, and therefore none of the offset voltages is added to the voltage reference. In summary,

$v_{\text{ref}}^*$  as the function of H is as follows:

$$v_{\text{ref}}^*(H) = M \sin \omega t, \qquad H = 0$$

$$M \sin \omega t + v_{\text{offset,inc}}, \qquad H = 1 \qquad (27)$$

$$M \sin \omega t + v_{\text{offset dec}}, \qquad H = -1.$$

The hysteresis band is selected based on the maximum voltage drop due to maximum loading condition in the first half cycle of the fundamental period. Setting appropriate hysteresis band avoids frequent third harmonic offset injection that affects the output quality. The midpoint capacitor voltage normally decreases to a certain level in the positive half cycle and then subsequently increases in the negative half cycle. This condition occurs when the motor is in motoring mode. The opposite condition is expected when the motor is in regenerative braking mode. Evaluating (25) for half cycle, from k = 1 to  $(1/2)N_k$ , yields the minimum limit for the hysteresis band. It is noted that D is evaluated with purely sinusoidal  $v_{ref}$  since voltage variation under a natural balancing condition is of interest.

On the other hand, in a case where the maximum voltage drop allowed and the switching frequency are already specified, the minimum capacitance required to fulfill that condition can be obtained as

$$\frac{{}^{N}k}{2}$$

$$1$$

$${}^{C}\min^{=} \frac{{}^{V}dc^{f}s^{\varepsilon}}{{}^{V}dc^{f}s^{\varepsilon}} k=1 i_{L}(k)D(k).$$

The proposed cell balancing method is recommended for use in the typical operating region (i.e., M=0.7 to 1) or at high speed to ensure that cell balancing works effectively with minimal output distortion. It is expected to work well when operated with full load current at the rated speed. However, its effectiveness might be affected when it is operated with full load current at a low speed down to zero. The reason is that voltage drop is significant at a low speed, and this forces the harmonic offset injection to work continuously, therefore degrading the output quality. Moreover, higher common-mode voltage is expected to appear in the system compared to normal operating conditions due to third harmonic offset injection. Nonetheless, this effect occurs temporarily only when the cell balancing takes place. The common-mode voltage generated by the proposed inverter is defined by (29), and it is measured between the neutral points of the load and the inverter

$${}^{v}dc^{f}s^{\varepsilon} k=1$$

$$1$$

$$v_{cm} = \overline{3}(v_{aN} + v_{bN} + v_{cN}). \tag{29}$$

#### VI. COMPARISON WITH OTHER MULTILEVEL INVERTERS

In order to evaluate the performance of the proposed inverter, comparison was made against the cascaded NPC with similar two-cell configuration. Comparison with cascaded NPC is made since it produces the same number of output levels per cell as that of proposed inverter. In comparison with the conventional CHB, the CHB is arranged into four-cell configuration, forming a nine-level CHB (9L-CHB) so as to produce the same output quality with the other two inverters. The comparison

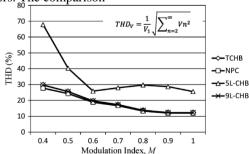

Fig. 14. Line voltage THD of the proposed inverter and other multilevel inverters.

#### A. Output Voltage Harmonics

Fig. 14 shows the total harmonic distortion (THD) of theline voltage for all inverters at different modulation indices. The THD of the proposed inverter, cascaded NPC, and the 9L-CHB are almost similar since they have the same output levels. However, a slight difference in THD occurs at low modulation indices particularly for the cascaded NPC as com-pared to the other two inverters. All the three inverters have almost linear relationship between the THD and the modulation indices, unlike the 5L-CHB which is very nonlinear. In general, the difference in THD between the three nine-level inverters and the 5L-CHB is about half, except for the modulation indices in the range of 0.5 < M < 0.7. In the typical operating region, 0.7 < M < 1, their THD varies from 12% to 17%, whereas for the 5L-CHB, its THD varies from 25% to 30%. The lower the THD, the lower the requirements of the output filter, thereby minimizing the overall system size

#### **B.** Conduction and Switching Power Losses

Conduction and switching power losses of all inverters were evaluated at three operating conditions (low, medium, and high-power factor). The first operating condition is when the inverters deliver 0.75 MW at 2.3 kV, with a 0.70 lagging power factor, second is when the inverters deliver 1 MW at 2.3 kV, with a 0.80 lagging power factor and the third operating condition is when delivering 1.25 MW at 2.3 kV, with 0.90 lagging power factor. The switching frequency is the same for all inverters for a fair comparison. For this purpose, all inverters were set to produce an effective switching frequency of 2 kHz for the line voltage output. Conduction losses of IGBT and diode can be approximated from their forward voltage drop,  $V_{\rm on,IGBT}$ ,  $V_{\rm on,D}$ , and the instantaneous current i(t) as takes into account the output quality of the inverters, total power losses, as well as the inverter specifications. In order to indicate the improvement in output quality and the additional power loss when using power cell with five-level output instead of three-level output, a comparison with the conventional five-level CHB (5L-CHB) in two-cell configuration was made as well.

$$\frac{I}{P \operatorname{cond} D} = \frac{1}{I - 0} V_{\operatorname{on,D}} i(t) dt \tag{31}$$

The device forward voltage drop is normally given as a function of current and can be obtained from the device's datasheets. They can be modeled using various types of curve fits such as power function  $(ax^b + c)$  and exponential function  $(ae^{bx} + ce^{dx})$  [41]. In this paper, Matlab Curve Fit toolbox is used for this purpose. The curve fit selection is based on the one that best represents the corresponding function over the desired range. The type of power switches selected for power loss estimation in this case is EUPEC IGBT (BSM300GA170DLC, 1700 V/300 A). It is chosen for its suitability and the availability of the required data. Modeling through the Matlab Curve Fit toolbox yields the forward voltage drop of the IGBT and the freewheeling diode as

$$V_{\text{on,IGBT}} = 2.099e^{0.001394i(t)} - 1.507e^{-0.01467i(t)}$$

(32)

$$Von, D = 1.563e^{0.001012i(t)} - 1.041e^{-0.01189i(t)}.$$

(33)

Substituting (32) and (33) into (30) and (31), respectively, yields the conduction power loss of IGBT and diode as

For switching power loss estimation, voltage drop across the switching device as well as the current flowing through it are sampled at each switching instant. From datasheet, switching energy loss is also given as a function of current for a certain dc-link voltage. Assuming a linear characteristic, the switching energy loss can be modeled proportional to the dc-link voltage in case if the dc-link voltage used in simulation is different from the dc-link voltage provided in the datasheet. Again, by apply-ing the curve fitting method, the equations which represent the switching energy loss for the IGBT,  $E_{\rm on,IGBT}$  and  $E_{\rm off,IGBT}$ , and the reverse recovery energy loss during turn-off,  $E_{\rm off}$  D for the diode are obtained as

$$E_{\text{on,IGBT}} = 47.83e^{0.003599i(t)} - 44.79e^{-0.004557i(t)}$$

(36)

$$E_{\text{off,IGBT}} = 0.552i(t)^{0.9023} - 0.2783$$

(37)

$$E_{\text{off},D} = 82.99e^{-0.0004465i(t)} - 81.62e^{-0.007217i(t)}. \tag{38}$$

Therefore, switching power losses for the IGBT,  $P_{\text{on,IGBT}}$  and  $P_{\text{off,IGBT}}$ , and turn-off power loss,  $P_{\text{off},D}$ , for the diode can be obtained by

$$P_{\text{on,IGBT}} = \frac{E^{1}}{T} - 47.83e^{0.003599i(t)}$$

$$= T - 44.79e^{-0.004557i(t)}$$

$$P_{\text{off,IGBT}} = \frac{E^{1}}{T} - 0.552i(t)^{0.9023} - 0.2783 - (40)$$

$$P_{\text{off,D}} = \frac{E^{1}}{T} - 82.99e^{-0.0004465i(t)}$$

(39)

$-81.62e^{-0.007217i(t)}$  (41)

The bidirectional switch diodes for the proposed inverter and the clamping diodes for the cascaded NPC are assumed to have similar characteristics with the IGBT free-wheeling diodes, and therefore the same equation is applied to estimate its power loss. Since the total power losses and the total output power are known, the inverter's efficiency can be obtained by

$$P_{\text{out}}$$

Efficiency(%) =

$$P_{\text{out}} + P_{\text{loss}} \times 100\%. \quad (42)$$

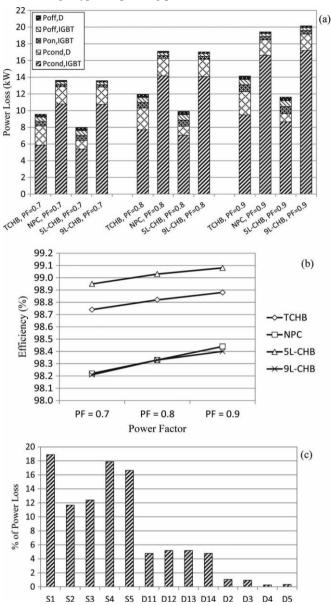

Among the three nine-level inverters, at PF = 0.9, the high-est power loss occurs in the 9L-CHB, followed by the cascaded NPC, and finally the proposed TCHB inverter as shown in Fig. 15(a). As expected, the 5L-CHB has the lowest power loss due to the least component count. Nevertheless, the total power losses of both the cascaded NPC and the 9L-CHB are almost similar at the other two operating conditions. To obtain nine-level output, the proposed inverter requires only 25% additional power switches compared to 5L-CHB, whereas for both cascaded NPC and 9L-CHB, 100%. The blocking voltage of each power switches in the cascaded NPC and 9L-CHB is relatively lower as compared to the proposed inverter due to its component arrangements. For this reason, the switching power losses of both inverters are also lower. However, the conduction power loss depends on the current that flows through power switches. The more power switches are used, the more conduction power loss will be, as experienced by both cascaded NPC and 9L-CHB inverters having four times the number of power switches of the proposed inverter.

The inverters' efficiencies at the corresponding three power factors are shown in Fig. 15(b). As the power factor increases, the efficiency of the inverters also increases as a result of more real power being effectively transferred with

respect to the power loss. From the figure, the inverters' efficiencies are found having an almost linear relationship with power factors. Con-sidering a typical operating power factor of an electric motors,

Fig. 15. (a) Comparison of total power losses at different power factors,

(b) comparison of the inverters' efficiencies, and (c) detailed power loss distribution among the switching devices in each power cell.

PF = 0.8 for comparison, the inverter's efficiency when using the 5L-CHB is 99.03%, the proposed inverter, 98.83%, and for the cascaded NPC and the 9L-CHB, they are both 98.33%. The efficiency's difference for the proposed inverter with respect to 5L-CHB is 0.2% while with the rest is 0.5%. Independent of the accuracy of absolute losses, a relative comparison is valid since the same model is used.

Fig. 15(c) shows the percentage power loss distribution among the switching devices in each power cell based on the average power switches' losses in one phase at P = 0.9. Note that  $S_2-D_2$ ,  $S_3-D_3$ ,  $S_4-D_4$ , and  $S_5-D_5$  are pairs that reside in one package. Diodes  $D_{11}$ ,  $D_{12}$ ,  $D_{13}$ , and  $D_{14}$  exist either in a discrete form or in a full-bridge package. This information is required in designing the appropriate heat sink as power losses among the devices are not symmetrically distributed. The highest conduction loss occurs in  $S_1$  with 18.88%, followed by

# TABLE III COMPARISON BETWEEN THE PROPOSED INVERTER AND THE OTHER MULTILEVEL INVERTERS

| Parameter                                 | Proposed<br>Inverter     | Cascaded<br>NPC               | n <sub>p</sub> L-<br>CHB   | (2n <sub>p</sub> -1)L-<br>CHB |

|-------------------------------------------|--------------------------|-------------------------------|----------------------------|-------------------------------|

| Phase voltage levels                      | 2np-1                    | $2n_{P}$ -1                   | $n_p$                      | $2n_{p}$ -1                   |

| Line voltage levels                       | 4np-3                    | $4n_{p}$ -3                   | 2np-1                      | $4n_{p}$ -3                   |

| Power cells per phase                     | $\frac{1}{2}(n_{p}-1)$   | $\frac{1}{2}(n_p-1)$          | $\frac{1}{2}(n_p-1)$       | $n_{p}$ -1                    |

| Power switches per phase                  | 2½ (n <sub>p</sub> -1)   | 4(n <sub>p</sub> -1)          | 2(n <sub>p</sub> -1)       | 4(n <sub>p</sub> -1)          |

| Bi-directional switch<br>-diodes / phase  | 2(n <sub>p</sub> -1)     | 1                             | -                          | 1                             |

| Clamping diodes                           | -                        | $2(n_p-1)$                    | -                          | -                             |

| Capacitors per phase                      | <i>n<sub>p</sub></i> -1  | $n_{p}$ -1                    | $\frac{1}{2}(n_p-1)$       | <i>np</i> -1                  |

| Isolated dc source per phase              | $\frac{1}{2}(n_p-1)$     | $\frac{1}{2}(n_p-1)$          | $\frac{1}{2}(n_{p}-1)$     | <i>n</i> <sub>p</sub> -1      |

| Power per cell                            | $2P_{nom}/$ $(3(n_p-1))$ | $\frac{2P_{nom}}{(3(n_p-1))}$ | $2P_{nom}/$ $(3(n_{p}-1))$ | $\frac{P_{nom}}{(3(n_p-1))}$  |

| Voltage measurement transducers per phase | n <sub>p</sub> -1        | n <sub>p</sub> -1             | $\frac{1}{2}(n_{p}-1)$     | <i>n</i> <sub>p</sub> -1      |

| Maximum voltage                           | 1 <i>pu</i>              | 1 <i>pu</i>                   | 1 <i>pu</i>                | 1 <i>pu</i>                   |

| Modulation method                         | CPS-<br>PWM              | CPS-<br>PWM                   | CPS-<br>PWM                | CPS-<br>PWM                   |

| Load voltage THD                          | Low                      | Low                           | High                       | Low                           |

| Efficiency                                | Medium                   | Low                           | High                       | Low                           |

| Output quality                            | High                     | High                          | Low                        | High                          |

$S_4$  and  $S_5$  with 17.88% and 16.64%, respectively. Next,  $S_3$  and  $S_2$  consume 12.40% and 11.67%, respectively. Bidirectional switch diodes ( $D_{11}$ ,  $D_{12}$ ,  $D_{13}$ , and  $D_{14}$ ) contribute to 19.94% of the total losses. This is then followed by  $D_2$  1.04%,  $D_3$  0.94%,  $D_5$  0.34%, and finally  $D_4$  0.27%.

A reduction in conduction power losses for TCHB is possible by using a bidirectional switch topology with two IGBTs connected with in common-emitter configuration [12]. In both directions, the current flows through one IGBT and one diode, rather than one IGBT and two diodes as in the presented con-figuration. Therefore, lower conduction losses can be achieved with increase in control complexity.

#### C. Inverter Specifications

The inverter specifications comparing the proposed inverter with the corresponding three inverters are given in Table III. The specifications are formulated in terms of the number of phase voltage levels  $n_p$  of the conventional CHB.

Since a minimum cascaded configuration requires two cells, therefore  $n_p$  counts from five levels onwards. The comparison includes the number of output levels, power switches, diodes, capacitors, isolated dc sources, and the power rating for each cell. The maximum voltage supported for all inverters is the same and so is the modulation method. For better output quality, use of the proposed inverter is better compared to the cascaded NPC and 9L-CHB with regard to the total power losses. The requirements for isolated dc power supply and voltage balancing for the proposed inverter and the cascaded NPC are the same, but the advantage of the proposed inverter is that it has lower total power losses. The use of 9L-CHB on the other hand though requires no voltage balancing, but it requires more isolated dc power supply by means of more transformers and therefore creates higher power losses as a whole.

Fig. 16. Scaled-down prototype.

Fig. 17. Hardware implementation: (a) the proposed inverter prototype and (b) phase-shifting transformers, induction motor load, and servo brake system

#### VII. EXPERIMENTAL VERIFICATION

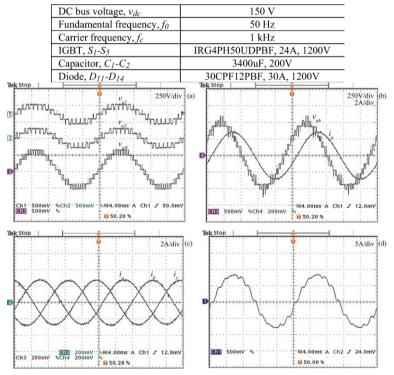

For verification, experimental tests were carried out where the scaled-down system shown in Fig. 16 used the inverter and load in Fig. 17(a) and (b), respectively. A TMS320F2812 DSP was used to generate the PWM signals and to implement the cell balancing mechanism. The inverter was supplied by a three-phase ac power supply through phase-shifting transform-ers. Each phase-shifting transformer provided two isolated dc sources with approximately 150-V dc voltage for the upper and the lower power cells. The modulation index was set to M=0.95. The specification of each cell is given in Table IV. Of the 30 IGBTs, six form the bidirectional switches. There are 12 dc capacitors, 24 diodes, six full-bridge rectifiers, and three phase-shifting transformers.

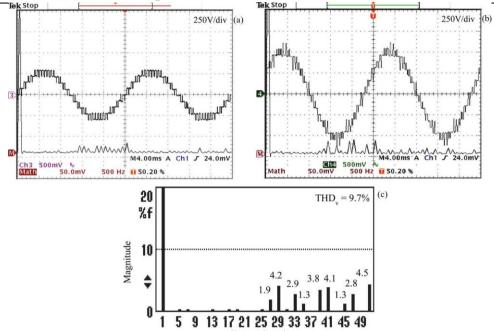

Fig. 18(a) shows the measured output voltage of phase a for each cell and the phase-to-neutral voltage, indicating uniform power distribution between the cells. A nine-level output was produced when the cells were cascaded in series. Full load line voltage and three-phase currents are shown in Fig. 18(b) and (c), respectively. In the line voltage, 17 levels were produced, thus providing high output quality. The output power measured was 1 kW, RMS voltage 355.9 V, RMS current 1.75 A, and frequency 50 Hz. Fig. 18(d) shows the main input current resembles a sinusoidal form as a result of using 12-pulse rectifier and phase-shifting transformer. The phase voltage and line voltage harmonics are shown in Fig. 19(a) and (b), respectively. The details of line voltage harmonics measured up to 50th harmonic order, a maximum order that can be measured using a Fluke 43B Power Analyzer, are shown in Fig. 19(c) with THD = 9.7%. The harmonics were found to be approx imately similar with those obtained in Fig. 5, thus validating the results.

In general, the effect of capacitor voltage imbalance in each cell is minimal for fixed frequency motor drive application. Fig. 20(a) shows the midpoint capacitor current  $i_C$  and the respective voltages,  $v_{C1}$  and  $v_{C2}$ , for Cell 1 in a full load constant-speed motor drive condition. The capacitor voltages balance (i.e., close to  $(1/2)v_{\rm dc}$ ) under normal conditions, indi-cating that  $I_{\rm avg}$  from the midpoint node is approximately zero, by means of natural balancing. A case where Cell 1 at first is unbalanced at  $t_0$  and then after applying the voltage balancing mechanism discussed at  $t_1$  gives the result shown in Fig. 20(b). Cell 2 with balancing control balances both capacitor voltages in spite of the Cell 1 initiated imbalanced, therefore validating the balancing mechanism. Another case where the balancing control of Cell 2 disabled is shown in Fig. 20(c). The tests were performed at partially loaded condition where both  $v_{\rm offset, bc}$  were set to 0.15.

# TABLE IV SPECIFICATION OF EACH POWER CELL FOR THE SCALED-DOWN PROTOTYPE

Fig. 18. Experimental results showing (a) each cell voltage and inverter phase voltage, (b) line voltage and current, (c) three-phase load current, and (d) main input current.

Fig. 19. Experimental results showing (a) phase voltage harmonics, (b) line voltage harmonics, and (c) detailed line voltage harmonics with its THD value.

Fig. 20. Experimental results showing (a) midpoint capacitor current and voltages of Cell 1, (b) capacitor voltage balancing of Cell 2 enabled, and

(c) capacitor voltage balancing of Cell 2 disabled.

#### VIII. CONCLUSION

In this paper, a cascaded multilevel inverter configuration based on a five-level TCHB power cell with multicarrier phase-shifted PWM modulation method, is presented. A new method to balance the midpoint capacitor voltage in each cell based on third harmonic offset injection was developed and tested. The output voltages of the proposed inverter were presented in a double Fourier integral form to determine their harmonics at various operating conditions. Detailed comparisons between the proposed inverter, cascaded NPC, 5L-CHB, and 9L-CHB in terms of power quality, power losses and inverter specifications were presented. From the findings, the proposed inverter is found potential not only for medium-voltage drive application but also other applications demanding higher output quality.

### REFERENCES

- [1] P. W. Hammond, "A new approach to enhance power quality for medium voltage AC drives," *IEEE Trans. Ind. Appl.*, vol. 33, no. 1, pp. 202–208, Jan./Feb. 1997.

- [2] F. Khoucha, S. M. Lagoun, K. Marouani, A. Kheloui, and M. El Hachemi Benbouzid, "Hybrid cascaded H-bridge multilevel-inverter induction-motor-drive direct torque control for automotive applications," *IEEE Trans. Ind. Electron.*, vol. 57, no. 3, pp. 892–899, Mar. 2010.

- [3] B. Ge, F. Z. Peng, A. T. de Almeida, and H. Abu-Rub, "An effective control technique for medium-voltage high-power induction motor fed by cascaded neutral-point-clamped inverter," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2659–2668, Aug. 2010.

- [4] H. Akagi and R. Kondo, "A transformerless hybrid active filter using three-level Pulsewidth Modulation (PWM) converter for a medium-voltage motor drive," *IEEE Trans. Power Electron.*, vol. 25, no. 6, pp1365–1374, Jun. 2010.

- [5] A. Varschavsky, J. Dixon, M. Rotella, and L. Moran, "Cascaded nine-level inverter for hybrid-series active power filter, using industrial con-troller," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2761–2767, Aug. 2010.

- [6] E. Villanueva, P. Correa, J. Rodriguez, and M. Pacas, "Control of a single-phase cascaded H-bridge multilevel inverter for grid-connected photovoltaic systems," *IEEE Trans. Ind. Electron.*, vol. 56, no. 11, pp4399–4406, Nov. 2009.

- [7] N. A. Rahim and J. Selvaraj, "Multistring five-level inverter with novel PWM control scheme for PV application," *IEEE Trans. Ind. Electron.*, vol. 57, no. 6, pp. 2111–2123, Jun. 2010.

- [8] P. Lezana and R. Aceiton, "Hybrid multicell converter: Topology and modulation," *IEEE Trans. Ind. Electron.*, vol. 58, no. 9, pp. 3938–3945, Sep. 2011.

- [9] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-point-clamped PWM inverter," *IEEE Trans. Ind. Appl.*, vol. IA-17, no. 5, pp. 518–523, Sep./Oct. 1981.

- [10] F. Z. Peng, J. W. McKeever, and D. J. Adams, "Cascade multilevel in-verters for utility applications," in *Proc. Int. Conf. Ind. Electron. Control Instrum.*, 1997, vol. 2, pp. 437–442.

- [11] M. F. Escalante, J. C. Vannier, and A. Arzande, "Flying capacitor mul-tilevel inverters and DTC motor drive applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 809–815, Aug. 2002.

- [12] S. Kouro, M. Malinowski, K. Gopakumar, J. Pou, L. G. Franquelo, B. Wu, J. Rodriguez, M. A. Perez, and J. I. Leon, "Recent advances and industrial applications of multilevel converters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2553–2580, Aug. 2010.

- [13] L. G. Franquelo, J. I. Leon, and E. Dominguez, "Recent advances in high-power industrial applications," in *Proc. IEEE Int. Symp. Ind. Electron.*, 2010, pp. 5–10.

- J. Rodriguez, L. G. Franquelo, S. Kouro, J. I. Leon, R. C. Portillo, M. A. M. Prats, and M. A. Perez, "Multilevel converters: An enabling technology for high-power applications," *Proc. IEEE*, vol. 97, no. 11, pp1786–1817, Nov. 2009.

- [15] H. Taghizadeh and M. T. Hagh, "Harmonic elimination of cascade mul-tilevel inverters with nonequal DC sources using particle swarm opti-mization," *IEEE Trans. Ind. Electron.*, vol. 57, no. 11, pp. 3678–3684, Nov. 2010.

- [16] W. Jin and D. Ahmadi, "A precise and practical harmonic elimination method for multilevel inverters," *IEEE Trans. Ind. Appl.*, vol. 46, no. 2, pp857–865, Mar./Apr. 2010.

- [17] N. Yousefpoor, S. H. Fathi, N. Farokhnia, and H. A. Abyaneh, "THD minimization applied directly on the line-to-line voltage of multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 59, no. 1, pp. 373–380, Jan. 2012.

- [18] J. Selvaraj and N. A. Rahim, "Multilevel inverter for grid-connected PV system employing digital PI controller," *IEEE Trans. Ind. Electron.*, vol. 56, no. 1, pp. 149–158, Jan. 2009.

- [19] G. Waltrich and I. Barbi, "Three-phase cascaded multilevel inverter using power cells with two inverter legs in series," *IEEE Trans. Ind. Electron.*, vol. 57, no. 8, pp. 2605–2612, Aug. 2010.

- [20] M. B. Smida and F. B. Ammar, "Modeling and DBC-PSC-PWM con-trol of a three-phase flying-

- capacitor stacked multilevel voltage source inverter," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2231–2239, Jul. 2010.

- [21] R. Naderi and A. Rahmati, "Phase-shifted carrier PWM technique for general cascaded inverters," *IEEE Trans. Power Electron.*, vol. 23, no. 3, pp1257–1269, May 2008.

- [22] S. Kouro, P. Lezana, M. Angulo, and J. Rodriguez, "Multicarrier PWM with DC-link ripple feedforward compensation for multilevel inverters," *IEEE Trans. Power Electron.*, vol. 23, no. 1, pp. 52–59, Jan. 2008.

- [23] B. Vafakhah, J. Salmon, and A. M. Knight, "A new space-vector PWM with optimal switching selection for multilevel coupled inductor invert-ers," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2354–2364, Jul. 2010.

- [24] M. M. Renge and H. M. Suryawanshi, "Three-dimensional space-vector modulation to reduce common-mode voltage for multilevel inverter," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2324–2331, Jul. 2010.

- [25] R. Rabinovici, D. Baimel, J. Tomasik, and A. Zuckerberger, "Series space vector modulation for multi-level cascaded H-bridge inverters," *IET Power Electron.*, vol. 3, no. 6, pp. 843–857, Nov. 2010.

- J. I. Leon, S. Vazquez, J. A. Sanchez, R. Portillo, L. G. Franquelo, J. M. Carrasco, and E. Dominguez, "Conventional space-vector modu-lation techniques versus the single-phase modulator for multilevel con-verters," *IEEE Trans. Ind. Electron.*, vol. 57, no. 7, pp. 2473–2482, Jul. 2010.

- [27] L. Yu, H. Hoon, and A. Q. Huang, "Real-time algorithm for minimiz-ing THD in multilevel inverters with unequal or varying voltage steps under staircase modulation," *IEEE Trans. Ind. Electron.*, vol. 56, no. 6, pp2249–2258, Jun. 2009.

- [28] E. Ozdemir, S. Ozdemir, and L. M. Tolbert, "Fundamental-frequency-modulated six-level diodeclamped multilevel inverter for three-phase stand-alone photovoltaic system," *IEEE Trans. Ind. Electron.*, vol. 56, no. 11, pp. 4407–4415, Nov. 2009.

- [29] S. Mukherjee and G. Poddar, "A series-connected three-level inverter topology for medium-voltage squirrel-cage motor drive applications," *IEEE Trans. Ind. Appl.*, vol. 46, no. 1, pp. 179–186, Jan./Feb. 2010

- [30] S. Khomfoi and L. M. Tolbert, "Fault diagnosis and reconfiguration for multilevel inverter drive using AI-based techniques," *IEEE Trans. Ind. Electron.*, vol. 54, no. 6, pp. 2954–2968, Dec. 2007.

- [31] P. Lezana and G. Ortiz, "Extended operation of cascade multicell con-verters under fault condition," *IEEE Trans. Ind. Electron.*, vol. 56, no. 7, pp 2697–2703, Jul. 2009.

- [32] M. A. Perez, P. Cortes, and J. Rodriguez, "Predictive control algorithm technique for multilevel asymmetric cascaded H-bridge inverters," *IEEE Trans. Ind. Electron.*, vol. 55, no. 12, pp. 4354–4361, Dec. 2008.

- [33] J. Dixon and L. Moran, "High-level multistep inverter optimization using a minimum number of power transistors," *IEEE Trans. Power Electron.*, vol. 21, no. 2, pp. 330–337, Mar. 2006.

- P. Sung-Jun, K. Feel-Soon, L. M. Hyung, and U. K. Cheul, "A new single-phase five-level PWM inverter employing a deadbeat control scheme," *IEEE Trans. Power Electron.*, vol. 18, no. 3, pp. 831–843, May 2003.

- [35] N. A. Rahim, M. F. M. Elias, and H. W. Ping, "A three-phase five-level inverter for DTC drives application," *IEICE Electron. Exp.*, vol. 8, no. 1, pp1–7, 2011.

- [36] M. Hiller, R. Sommer, and M. Beuermann, "Medium-voltage drives," *IEEE Ind. Appl. Mag.*, vol. 16, no. 2, pp. 22–30, Mar./Apr. 2010.

- [37] B. Wu, *High-Power Converters and AC Drives*. New York: IEEE Press, 2006.

- [38] B. P. McGrath and D. G. Holmes, "Multicarrier PWM strategies for multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 858–867, Aug. 2002.

- [39] H. Sepahvand, L. Jingsheng, and M. Ferdowsi, "Investigation on capacitor voltage regulation in cascaded H-bridge multilevel converters with funda-mental frequency switching," *IEEE Trans. Ind. Electron.*, vol. 58, no. 11, pp. 5102–5111, Nov. 2011.

- [40] P. Zhiguo and P. F. Zheng, "A sinusoidal PWM method with voltage bal-ancing capability for diode-clamped five-level converters," *IEEE Trans. Ind. Appl.*, vol. 45, no. 3, pp. 1028–1034, May/Jun. 2009.

- [38] C. Govindaraju and K. Baskaran, "Efficient sequential switching hybrid-modulation techniques for cascaded multilevel inverters," *IEEE Trans. Power Electron.*, vol. 26, no. 6, pp. 1639–1648, Jun. 2011.

**Nasrudin Abd. Rahim** (M'89–SM'08) was born in Johor, Malaysia, in 1960. He received the B.Sc. (Hons.) and M.Sc. degrees from the University of Strathclyde, Glasgow, U.K., and the Ph.D. de-gree from Heriot-Watt University, Edinburgh, U.K., in 1995.

Currently, he is a Professor with the Department of Electrical Engineering, University of Malaya, Kuala Lumpur, Malaysia, and is also the Director and Founder of the UM Power Energy Dedicated Ad-vanced Center, University of Malaya. His research interests include power electronics, real time control systems, electrical drives, and

interests include power electronics, real-time control systems, electrical drives, and renewable energy systems.

Dr. Nasrudin is a Fellow of the Academy of Sciences Malaysia and the Institution of Engineering and Technology, and is a Chartered Engineer.

**Mohamad Fathi Mohamad Elias** (S'09) was born in Sarawak, Malaysia, in 1981. He received the B.Eng. (Hons.) degree in electrical engineering and the M.Eng. degree from University of Malaya, Kuala Lumpur, Malaysia, in 2003 and 2007, respectively, where he is currently working toward the Ph.D. degree in electrical engineering in the UM Power Energy Dedicated Advanced Center.

His research interests include power electronics and electrical drives.

**Wooi Ping Hew** (M'06) received the B.Eng. and M.Eng. degrees from the Universiti Teknologi Malaysia, Malaysia, in 1981 and 1991, respectively, and the Ph.D. degree from University of Malaya, Kuala Lumpur, Malaysia, in 2000.

Currently, he is a Professor with the Department of Electrical Engineering, University of Malaya, where he is also with the UM Power Energy Ded-icated Advanced Center, University of Malaya. His research interests include electrical drives, electri-cal machine design, and application of fuzzy logic/

neural network to electrical-machine-related applications.

Dr. Hew is a member of the Institution of Engineering and Technology and is a Chartered Engineer.